Principiul de funcționare și varietatea de factori declanșatori - studopediya

Baza oricărui bistabil (engl. - „Trigger“ sau „flip-flop“) este o diagramă a două elemente logice care sunt acoperite de feedback-ul pozitiv (adică semnalele de la ieșirile furnizate intrări). Ca rezultat al acestui circuit de comutare poate fi într-una din cele două stări stabile, în care rămân pe termen nelimitat, până când acesta este alimentat.

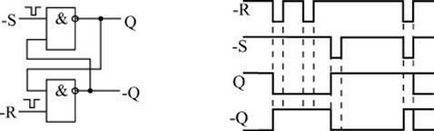

Fig. Schema de celule de declanșare

Un exemplu de astfel de circuit (așa-numitele celule flip-flop) în două ȘI cu două intrări-NO elemente este prezentată în Fig. 7.1. În schema există două intrare inversă: -R - reset (din limba engleză Reset), și -S - instalare (din setul de limba engleză), precum și două ieșiri: ieșire directă Q și -Q ieșire inversată.

impulsuri negative, trebuie să ajungă la intrările sale nu sunt, în același timp, pentru funcționarea corectă a circuitului. Sosirea impulsului la intrare traduce unitatea de ieșire R -Q în stat și, deoarece, în acest caz -S unitate de semnal, ieșirea Q devine zero. Ca urmare a semnalului Q este alimentat printr-un circuit de feedback la intrarea membrului inferior. Prin urmare, chiar și după pulsul la starea -R circuitul de intrare nu se modifică (rămâne la zero, Q, -Q rămâne pe unitate). In mod similar, atunci când impulsul de intrare sosire -S ieșire Q per unitate, iar -Q ieșire - zero. Aceste două stări stabile ale celulelor de declanșare pot fi stocate pe termen nelimitat, până când următorul impuls de intrare - cu alte cuvinte, circuitul are o memorie.

Dacă ambele impulsul de intrare va veni strict simultan, punctul de acțiune al acestor impulsuri la ieșirile ambelor semnale vor fi izolate, iar după ieșirile de impulsuri de intrare se încadrează în mod aleatoriu în una din cele două stări stabile. În mod similar, la întâmplare una din cele două stări stabile ale celulei flip-flop atunci când va fi selectat puterea. Diagrama de sincronizare a unei celule de declanșare este prezentată în Fig.

Tabel. Tabelul de adevăr al celulei de declanșare

Declanșatorul de intrare este împărțit în informații și de control.

intrările de date sunt indicate după cum urmează:

S - o intrare pentru setarea la starea „1“;

R - o intrare pentru setarea la starea „0“;

J - o intrare pentru setarea la starea „1“ într-un declanșator universal;

intrare K- pentru stabilirea stării de „0“, într-un declanșator universal;

T - de numărare (partajat) de intrare;

D - o intrare pentru setarea la starea „1“ sau starea „0“.

Triggerele pot fi clasificate în funcție de procesul de primirea informațiilor, principiul de construcție, funcționalitate.

Cu titlu informativ recepție declanșatoare sunt împărțite în sincron și asincron. declanșatoare asincrone observa semnalele de informare și de a reacționa la ele, la momentul apariției a intrărilor de declanșare. declanseaza sincronă reacționează la semnalele de informație în prezența semnalului permit asupra speciale de control de intrare C, intrare numita sincronizare. Synchronous declanseaza declanșatoare sunt împărțite în control static și dinamic de intrare S. Declanseaza semnalelor de informație de control static percepute atunci când sunt aplicate la C - 1 nivel de intrare (linia C - intrare). Declanseaza cu semnale de control dinamic la percep conformationala semnal de modificare C - intrare la 0 la 1 (dinamic C directă - intrare) sau de la 1 la 0 (invers dinamic C - intrare).

Conform principiului clădirii declanșează un control static sunt împărțite în o singură etapă și în două etape. Single declanșatoare etapă se caracterizează printr-o etapă de stocare a informațiilor, sunt două etape de informare de declanșare stocare pas. Inițial, informația este înregistrată în prima etapă, și apoi rescris în al doilea, și apare la ieșire.

Un declanșator cu două trepte notate CT.

Prin funcționalitate declanșatoare sunt împărțite în următoarele clase:

• set state separate 0 și 1 (RS - declanșatoare);

• universal (JK - flip-flops)

• primirea de informații cu o intrare D (D-declanșatori)

cu o intrare T numărabilă (T - declanșatori).

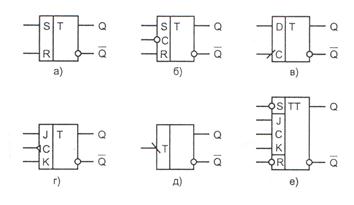

Mai jos sunt simboluri grafice (ASB) declanșatoare luate de sistem ESKD:

A) asincron RS - declanșare sincron;

B) cronometrat RS - declanșare. Sincronizarea se realizează 0 logic;

B) D - flip-flop, care este declanșat pe frontul crescător 0,1;

R) JK - flip-flop, care este declanșat pe muchie 1, 0;

D) T - flip-flop, care este declanșat pe muchie 1, 0;

E) în două etape JK - declanșator cu intrări de setare împărțit la zero (R) și un singur (S) stat.

Funcționarea declanșează descrise tabelul de tranziție (adevăr): „ISH“ - înseamnă modul de stocare (starea inițială sau nemodificată).

„Neopren“ - înseamnă că ieșirile de stat indefinit, adică, combinația de semnal R = S = 1 este interzisă ...

W - T = declanșare atunci când declanșatorul 1 trece în starea Qn care poate fi inversat - 1 (modul de numărare). JK - declanșare cu J = K = 1 trăgaciul se deplasează în stare Qn inversat - 1 (Mod numărare). Qn - 1 - stare de ieșire înainte de apariția semnalelor de informație.